# Toward 300 mm Wafer-Scalable High-Performance Polycrystalline Chemical Vapor Deposited Graphene Transistors

Somayyeh Rahimi,<sup>†</sup> Li Tao,<sup>†</sup> Sk. Fahad Chowdhury,<sup>†</sup> Saungeun Park,<sup>†</sup> Alex Jouvray,<sup>‡</sup> Simon Buttress,<sup>‡</sup> Nalin Rupesinghe,<sup>‡</sup> Ken Teo,<sup>‡</sup> and Deji Akinwande<sup>\*,†</sup>

<sup>†</sup>Department of Electrical and Computer Engineering, The University of Texas at Austin, Austin, Texas 78758, United States and <sup>‡</sup>Aixtron Ltd., Anderson Road, Swavesey, Cambridge, CB24 4EQ, U.K.

**ABSTRACT** The largest applications of high-performance graphene will likely be realized when combined with ubiquitous Si very large scale integrated (VLSI) technology, affording a new portfolio of "back end of the line" devices including graphene radio frequency transistors, heat and transparent conductors, interconnects, mechanical actuators, sensors, and optical devices. To this end, we investigate the scalable growth of polycrystalline graphene through chemical vapor deposition (CVD) and its integration with Si VLSI technology. The large-area Raman mapping on CVD polycrystalline graphene on 150 and 300 mm wafers

reveals >95% monolayer uniformity with negligible defects. About 26 000 graphene field-effect transistors were realized, and statistical evaluation indicates a device yield of  $\sim$ 74% is achieved, 20% higher than previous reports. About 18% of devices show mobility of >3000 cm<sup>2</sup>/(V s), more than 3 times higher than prior results obtained over the same range from CVD polycrystalline graphene. The peak mobility observed here is  $\sim$ 40% higher than the peak mobility values reported for single-crystalline graphene, a major advancement for polycrystalline graphene that can be readily manufactured. Intrinsic graphene features such as soft current saturation and three-region output characteristics at high field have also been observed on wafer-scale CVD graphene on which frequency doubler and amplifiers are demonstrated as well. Our growth and transport results on scalable CVD graphene have enabled 300 mm synthesis instrumentation that is now commercially available.

**KEYWORDS:** polycrystalline graphene  $\cdot$  CVD  $\cdot$  wafer-scale integration  $\cdot$  field-effect transistors  $\cdot$  device performance statistics  $\cdot$  mobility  $\cdot$  analog applications

raphene, a two-dimensional sheet of carbon atoms, has attracted research attention on a wide variety of high-performance device applications owing to its remarkable electronic, optical, and mechanical properties.<sup>1–13</sup> The largest application of graphene will likely be realized when combined with ubiquitous Si complementary metal-oxide-semiconductor (Si CMOS) technology. However, the integration of graphene with Si CMOS has been a great challenge due to the lack of a reliable large-scale preparation scheme for graphene that preserves the high performance of the chip-scale graphene films. Several different methods have been proposed for growing wafer-scale graphene, including epitaxial growth on SiC wafers,<sup>8,14</sup> reduction of graphene oxide, <sup>15,16</sup> chemical vapor deposition (CVD) on metal thin films,<sup>9,17</sup> and recently CVD on hydrogen-terminated

single-crystalline germanium surfaces.<sup>10</sup> Among these methods, the CVD mechanism is the most well-studied and reproducible mechanism and is more likely to be compatible with Si very large scale integrated (VLSI) technology. The CVD mechanism can be achieved on metal foils or films based on Cu, where the former (Cu foils) has been the most widely adopted method. However, the CVD growth of graphene on inexpensive and widely available Cu foils, while having great potential for roll-to-roll or flexible technology,<sup>7,18,19</sup> is not compatible with the Si CMOS integration process due to the lack of mechanical rigidity of Cu foils. On the other hand, deposited Cu films on standard oxidized silicon wafers that afford integration compatibility with Si VLSI previously suffered from uncontrolled polycrystalline structure that leads to defective graphene formation with inferior

\* Address correspondence to D. Akinwande: deji@ece.utexas.edu.

Received for review July 14, 2014 and accepted September 8, 2014.

Published online September 08, 2014 10.1021/nn5038493

© 2014 American Chemical Society

VOL.8 • NO.10 • 10471-10479 • 2014

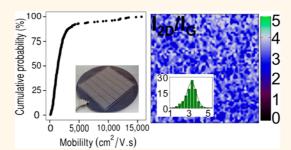

Figure 1. Large-area Raman mapping of graphene on 150 mm Cu substrates reveals >95% monolayer continuity and an average value of  $\sim$ 2.62 for  $I_{2D}/I_{G}$ . The average value and the standard deviation of  $I_{2D}/I_{G}$  for each Raman map are presented. The view of the 150 mm wafer, used for this study, is shown at the top center of the image. The scale bar represents 200  $\mu$ m.

performance, such as lower carrier mobility.<sup>20</sup> Recent progress revealed the growth of monolayer graphene with minimal defects by controlling parameters such as hydrogen or oxygen on the Cu surface to promote Cu(111) crystallization or to suppress graphene nucleation, resulting in the growth of large graphene domains across several Cu grains, respectively.<sup>21,22</sup> These studies suggest that the high quality of graphene synthesized on polycrystalline films is sufficient for device applications. Most remarkably, transport studies on polycrystalline graphene reported here offer higher peak mobility than recent reports on single-crystalline synthesized graphene.<sup>8,10</sup> This counterintuitive observation can be understood from theoretical and experimental analysis that suggests grain boundary scattering is likely not the dominant mechanism limiting charge transport in wafer-scale graphene devices.23-25

In this article, we demonstrate the scalability of CVD graphene growth on polycrystalline Cu films from 100 to 300 mm substrates and its integration with Si substrates for future VLSI integrated technology. The synthesized polycrystalline graphene offers a superior carrier transport characteristic to existing poly- or single-crystalline wafer-scale reports. Monolayer graphene coverage of >95% is achieved on 300 mm wafer substrates with negligible defects, confirmed by Raman mapping. Approximately 26 000 back-gated graphene field-effect transistors (GFETs) are realized by a CMOS-compatible fabrication method, and statistical evaluation of the electrical characteristics reveals

a device yield of  $\sim$ 74% was achieved, comparable to the 70-80% yield of early (1960s) silicon wafer-scale device development.<sup>26</sup> An average carrier mobility of  $\sim$ 2113 cm<sup>2</sup>/(V s) was achieved, and notably  $\sim$ 18% of devices showed mobility of >3000  $\text{cm}^2/(\text{V s})$ . The peak mobility observed here is  $\sim$ 40% higher than the equivalent value reported for wafer-scale single-crystalline graphene so far. Low-temperature transport measurements show phonon scattering affects higher-mobility GFETs and impurity scattering is dominant for lowermobility devices, suggesting that lowering the residual impurity level is critical for achieving highperformance devices. We also demonstrate frequency doubler and signal amplifier functions from wafer-scale devices as practical examples for large-scale analog electronics.

# **RESULTS AND DISCUSSION**

The CVD graphene growth, demonstrated on 100 mm wafers<sup>12</sup> at 975 °C, has been scaled to 150 mm (Figure 1) and 300 mm (Figure 2) wafers using a CH<sub>4</sub> precursor at 750–800 °C (see Methods and Figure S1 for growth details). The reduction in the growth temperature has been achieved by employing both a substrate and a showerhead heater, leading to a more uniform heating of the gas flux in the vertical and lateral directions. The homogeneous heat distribution in the growth chamber is critical in order to produce graphene with low defect density and uniform quality all across the 300 mm wafer (see the Supporting Information). A hydrogen-saturated annealing step is

VOL.8 • NO.10 • 10471-10479 • 2014

www.acsnano.org

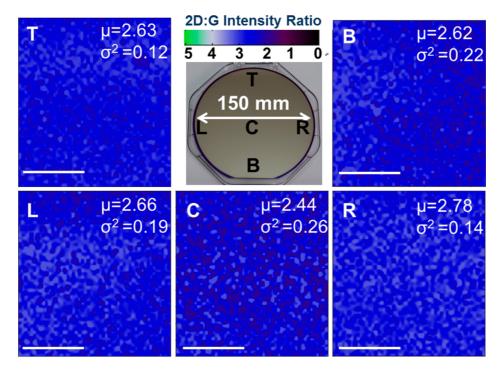

Figure 2. (a)  $I_D/I_G$  and (b)  $I_{2D}/I_G$  Raman mapping at the center of a 300 mm growth substrate shows the high quality of graphene with a negligible defect peak. The insets are the histogram distributions of  $I_D/I_G$  and  $I_{2D}/I_G$ , with average values of 0.2 and 3.4, respectively. Scale bars are 50  $\mu$ m. (c) View of the 300 mm substrate used for this study. Arrow shows the direction of the Raman spot scans. (d)  $I_{2D}/I_G$  of Raman spot scans performed along the radial direction of the 300 mm substrate. The inset shows a representative Raman spectrum.

performed on the uniformly heated substrate, to promote the growth of hexagonal-phase Cu(111) structures (~> 10  $\mu$ m), and is followed by the growth step with CH<sub>4</sub> and without H<sub>2</sub>, which subsequently leads to the formation of scalable monolayer graphene with negligible defect density.<sup>21</sup> A set of images of 100–300 mm Si substrates used for this study is shown in Figure S2.

To verify the uniformity of the grown film on 150 and 300 mm substrates, Raman spectroscopy mapping was employed (see Methods). Figure 1 shows the mapping results collected from five different locations of the 150 mm substrate (500  $\mu$ m × 500  $\mu$ m mapping area). The 2D:G intensity ratio ( $l_{2D}/l_G$ ) on the mapped area shows an average value of ~2.62 with a standard deviation of 0.19. Mapping of the D:G intensity ratio ( $l_D/l_G$ ) on the same locations, presented in Figure S3, shows an average value of 0.06 with a deviation of 0.008, indcating the good structural quality of the synthesized graphene. On the basis of the statistical analysis of the Raman mapping data, monolayer graphene was achieved on 150 mm substrates with negligible defects.

Similarly, Raman mapping confirmed uniform monolayer graphene with a negligible defect peak and average values of 0.2 and 3.4 for  $I_D/I_G$  and  $I_{2D}/I_G$  on an area of 150  $\mu$ m × 150  $\mu$ m at the center of a 300 mm substrate (Figure 2a and b). The view of the 300 mm substrate used for this study and the results of the Raman spot scans as a function of distance from the center of the wafer are shown in Figure 2c and d. An average value of 2.6 is achieved for  $I_{2D}/I_G$  spot scans along the radial direction, comparable to the average  $I_{2D}/I_G$  on a 150 mm substrate, confirming the scalability of the growth process.

Table 1 summarizes the results of Raman spectroscopy scanning obtained here and compares it to other extracted and reported values of  $l_{2D}/l_G$  and  $l_D/l_G$  from wafer-scale CVD and epitaxially grown poly- and single-crystalline graphene. The comparison shows the saturated hydrogen annealing and methane-only precursor for the growth step in this study leads to a larger value of  $l_{2D}/l_G$ , while  $l_D/l_G$  does not exhibit a significant increase with scale-up in the growth wafer substrate.

The wafer-scale graphene preserves its high quality after transfer from a 100 mm growth substrate to the same wafer size constrained by our 100 mm microelectronic device fabrication cleanroom. The Raman spot scans, taken from five different locations on the 100 mm SiO<sub>2</sub>/Si substrate after the transfer, show a negligible defect peak and good quality across the 100 mm wafer (Figure 3a). For instance, the average value of  $I_{2D}/I_{G}$  after the transfer, presented in Figure 3b, shows a narrow distribution within 2.5–3 with negligible

TABLE 1. Comparison of the Material and Electrical Properties of Reported Wafer-Scale Polycrystalline and Single-Crystalline Graphene

| substrate/size (mm)      | I <sub>2D</sub> /I <sub>G</sub> | I <sub>D</sub> /I <sub>G</sub> | $\mu_{\rm max}$ (cm²/(V s)) | residual carrier density ( $	imes$ 10 <sup>11</sup> cm <sup>-2</sup> ) | ref                     |

|--------------------------|---------------------------------|--------------------------------|-----------------------------|------------------------------------------------------------------------|-------------------------|

| Cu film/100—300          | 2.6-3.3                         | 0.03-0.22                      | 15 660                      | 3.4-29                                                                 | this work               |

| Cu film/200              | 1.8                             | 0.13                           | 3800                        | 1.49 <sup>d</sup>                                                      | Gao, 2014 <sup>11</sup> |

| Ge(110) <sup>a</sup> /50 | 3.5                             | 0.03                           | 10 600                      | $3^d$                                                                  | Lee, 2014 <sup>10</sup> |

| SiC <sup>a</sup> / 100   | 1.6-1.9                         | 0 <sup>b</sup>                 | 2700                        | 10—100                                                                 | Kim, 2013 <sup>8</sup>  |

| Cu film/100              | 3                               | 0.2                            | 4900                        | 10 <sup><i>d</i></sup>                                                 | Tao, 2012 <sup>12</sup> |

| Cu film/150              | 4.5                             | 0.3                            | 23 000 <sup>c</sup>         | 10—40                                                                  | Heo, 2011 <sup>13</sup> |

| Ni/Cu films/75           | 3.5                             | 0.25                           | 3000                        | 28 <sup><i>d</i></sup>                                                 | Lee, 2010 <sup>9</sup>  |

<sup>*a*</sup> Single-crystalline substrates. <sup>*b*</sup> Graphene structures always contain a finite defect peak.<sup>37</sup> No defect peak was reported; as such, this reported value is likely to be incorrect. <sup>*c*</sup> Only 3% of measured devices showed  $\mu > 3000 \text{ cm}^2/(\text{V s})$ . <sup>*d*</sup> Data are based on single device report.

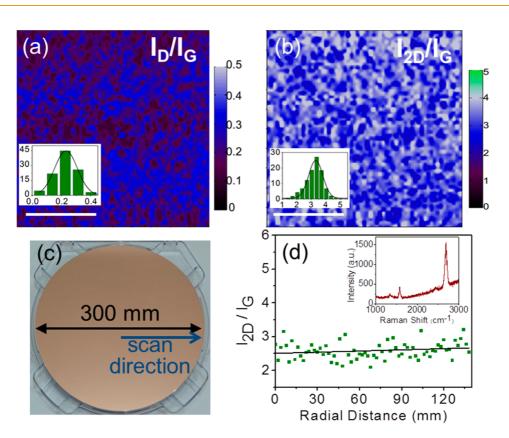

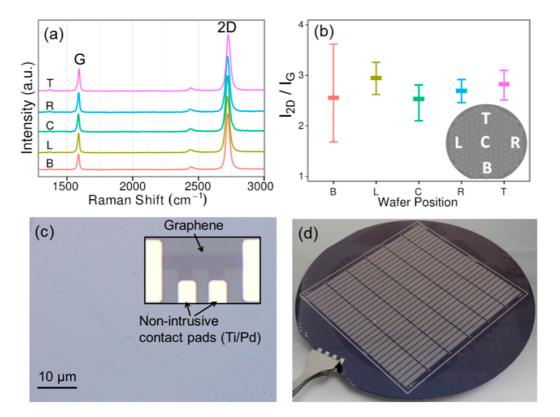

Figure 3. (a) Raman spot scans of graphene after transfer to a 100 mm wafer showing negligible defect mode. The Raman spectra were normalized to the intensity of the 2D peak before stacking. (b) The statistical distribution of  $I_{2D}/I_G$  at five different locations on the 100 mm substrate shows good uniformity. (c) Optical image of graphene after the transfer. The inset shows a representative four-probe device. (d) View of 26 000 fabricated graphene devices on a 100 mm Si wafer.

defect ratio. A microscopic image of the graphene film after the transfer to  $SiO_2/Si$  substrate and the view of the 100 mm substrate after device fabrication are presented in Figure 3c and d.

Using a standard UV photolithography method, about 26 000 back-gated GFETs were fabricated on the transferred film (see Methods for fabrication steps). A variety of two- and four-probe back-gated GFETs with varying length and width (3, 6, and 9  $\mu$ m) were fabricated to investigate the electrical characteristics of the graphene channels. An optical image of a fabricated four-probe device ( $W = 3 \mu$ m,  $L = 9 \mu$ m) with nonintrusive contact pads is shown in the inset of Figure 3c.

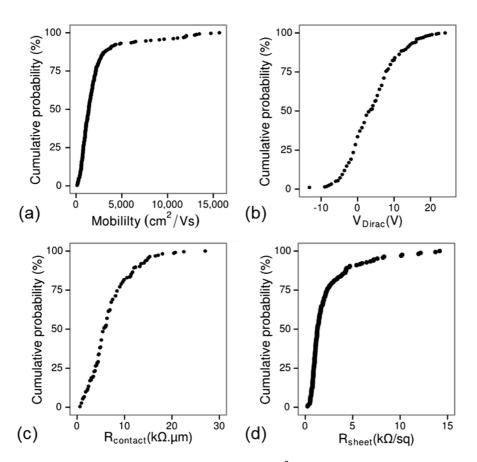

Due to the long time required for performing the field-effect modulation by sweeping the back-gate bias in the [-30, 30] V range on every fabricated GFET, a statistical study was carried out on 550 randomly chosen GFETs across the wafer. A device yield of 74% with a confidence interval (margin of error) of 3.7% was achieved, a 20% higher yield than prior work.<sup>13</sup> The low value of the confidence interval indicates that if all devices had been tested, the device yield would be in the range of 74  $\pm$  3.7% with 95% probability (see Supporting Information). The distributions of the field-effect mobility, Dirac voltage ( $V_{\text{Dirac}}$ ), contact resistance ( $R_{\text{contact}}$ ), and sheet resistance ( $R_{\text{sheet}}$ ) under ambient conditions, in the form of cumulative

VOL.8 • NO.10 • 10471-10479 • 2014

Figure 4. Cumulative plots of (a) field-effect mobility (mean: 2113 cm<sup>2</sup>/(V s)), (b) V<sub>Dirac</sub> (mean: 6.2 V), (c) R<sub>Contact</sub> (mean: 2116  $\Omega \cdot \mu$ m), and (d)  $R_{\text{sheet}}$  (mean: 2600  $\Omega$ /sq). The device arrays have dimensions in the micrometer range, and all measurements are performed under ambient conditions.

probability plots, are presented in Figure 4a-d. The average value of the field-effect mobility, which is extracted using a widely accepted diffusive transport model,<sup>27</sup> is observed to be 2113 cm<sup>2</sup>/(V s), and most notably the mobility of 5% of GFETs is above 10 000  $\text{cm}^2/(\text{V s})$ , 5 times higher than prior results over the same range.<sup>13</sup> These values of mobility are comparable to the mobility values extracted from high-quality chip-scale polycrystalline CVD graphene samples<sup>25,28</sup> and epitaxially grown graphene on a wafer-scale singlecrystalline substrate.<sup>8,10</sup> The high percentage of devices with  $\mu > 10\,000 \text{ cm}^2/(\text{V s})$  achieved here is further evidence of the previous reports that high carrier mobility mainly correlates with graphene domain structures generated during the synthesis process rather than graphene domain size.23-25 The statistical 5–95% mobility and  $R_{contact}$  distribution at five different locations of a 100 mm wafer are presented in Figure S4a,b. The comparison between Figure S4a and b suggests that regions with lower average R<sub>contact</sub> show higher average mobility values. Considering the Raman spot scans, after the transfer (Figure 3b), the variation of mobility and  $R_{contact}$  distribution at different locations on the wafer after the fabrication process is believed to be mainly due to the resist residue rather than initial differences in the quality of graphene.<sup>29</sup> The high value of the average mobility, achieved here, is a promising indicator that the likely success of ongoing integration research in addressing the sources of electrical variability, coming from the residue of the transfer and fabrication process, will result in uniformly high-performance graphene devices at wafer scale. It is also worth noting here that the dimensions of the largest channels (3  $\mu$ m  $\times$  9  $\mu$ m) are smaller than the average domain size of the synthesized film ( $\sim$ > 10  $\mu$ m) obtained by our growth process. We expect that, with similar likelihood, the transistor channels traverse graphene domain boundaries or are contained within a single graphene domain.

The Dirac voltage, presented in Figure 4b, is narrowly distributed around 0  $\pm$  10 V and shows an average value of 6.2 V. The positive and negative shifts of  $V_{\text{Dirac}}$ around 0 V are indicative of the slight p- and n-doped channels, which are believed to be caused by the net effect of moisture adsorption and photoresist impurities from the fabrication process<sup>30–32</sup> and the doping from the SiO<sub>2</sub> substrate.<sup>33</sup> The contact resistance, obtained by fitting the channel resistance versus the gate voltage, has an average value of 2116  $\Omega \cdot \mu m$ , comparable to the reported Pd-based graphenemetal contacts fabricated by electron-beam

VOL.8 • NO.10 • 10471-10479 • 2014 A

www.acsnano.org

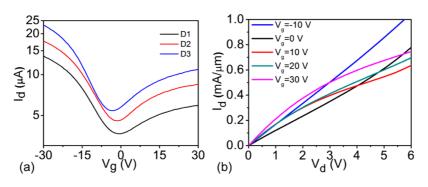

Figure 5. (a) Channel current vs gate voltage for three representative two-probe devices (D1:  $W = 3 \mu m$ ,  $L = 3 \mu m$ ; D2:  $W = 6 \mu m$ ,  $L = 3 \mu m$ ; and D3  $W = 9 \mu m$ ,  $L = 3 \mu m$ ) at room ambient and  $V_d = 100 \text{ mV}$ ; mobilities are in the 2000–2500 cm<sup>2</sup>/(V s) range. (b)  $I_d - V_d$  characteristics of a high-mobility device ( $W = 6 \mu m$ ,  $L = 3 \mu m$ ),  $\mu = 10\,600 \text{ cm}^2/(\text{V s})$ , and  $V_{\text{Dirac}} = 0 \text{ V}$ , at different backgate voltage showing the intrinsic soft saturation of graphene.

(e-beam) lithography,<sup>18,29,34</sup> suggesting that the performance of the graphene—metal contact does not change drastically when the low-throughput e-beam lithography method is replaced by the CMOS-compatible UV photolithography at wafer scale. The sheet resistance, measured at floating back-gate potential, has an average value of 2600  $\Omega$ /sq, comparable to  $1-2 k\Omega$ /sq reported for the chip-scale CVD polycrystalline graphene devices.<sup>35</sup> The cumulative plot of sheet resistance measured at back-gate voltage 0 V and average  $V_{\text{Dirac}}$  of 6 V, shown in Figure S5, follows the same distribution of  $R_{\text{sheet}}$  at floating back-gate potential with larger average values, indicating smaller carrier density.

In Table 1 we compare the peak mobility  $(\mu_{max})$  at T = 300 K and the impurity density obtained here with other wafer-scale poly- and single-crystalline CVD and epitaxially grown graphene reported previously. The impurity densities listed in Table 1 for Kim et al.,<sup>8</sup> Lee et al.,<sup>10</sup> and Heo et al.<sup>13</sup> are exact reported values, and the listed values for Lee et al.,<sup>9</sup> Gao et al.,<sup>11</sup> and Tao et al.<sup>12</sup> are extracted through the equation  $n \simeq C_{ox} | V_{q} V_{\text{Dirac}}/e$ , for nonzero  $V_{\text{Dirac}}$ , where  $V_q$  and e are the gate bias and the electron charge,  $C_{ox} = \varepsilon_{ox}/t_{ox}$  is the gate capacitance per area, and  $\varepsilon_{ox}$  and  $t_{ox}$  are the gate dielectric and thickness, respectively.<sup>36</sup> The impurity density of measured devices here, which falls in the range of  $(3.4-29) \times 10^{11}$  cm<sup>-2</sup>, is extracted through a diffusive transport model and indicates the relatively low concentration of impurities in the synthesized graphene. The value of  $\mu_{max}$  is one of the highest reported values for polycrystalline graphene so far and is  $\sim$ 40% higher than the best value reported for single-crystalline graphene. Note that except for the data reported in this work and in Lee et al.,<sup>9</sup> Heo et al.,<sup>13</sup> and Lee et al.,<sup>10</sup> the rest of the reported values in Table 1 are based on a limited number of measurements performed on devices fabricated using e-beam lithography.

In the discussion to follow, we further evaluate the results of the electrostatic and transport properties of GFETs at low temperature and room ambient.

Figure 5a presents the drain current  $(I_d)$  of three representative GFETs, with varying width (3, 6, and 9  $\mu$ m) and uniform length (3  $\mu$ m), as a function of applied gate voltage at  $V_{\rm d}$  = 100 mV and room ambient. The asymmetry between the hole and electron transport, observed mainly for two-probe GFETs in the 78-300 K range, possibly originates from pinning of the charge density below the metal contacts<sup>38</sup> and the higher scattering rates of electrons in the channel by the impurities.<sup>30,31</sup> Figure 5b presents  $I_d$  versus drain voltage ( $V_d$ ) characteristics of a two-probe GFET (W =6  $\mu$ m, L = 3  $\mu$ m) at different V<sub>a</sub>. The soft saturation region, which reflects the ambipolar nature of graphene, was previously reported for exfoliated flakes mainly with top-gated structures.<sup>39-41</sup> We recently reported this effect on our high-mobility inductively heated synthesized CVD graphene on a 300 nm SiO<sub>2</sub> back-gate dielectric.<sup>6</sup> The current saturation effect is shown to be pronounced in high-mobility GFETs with low contact resistance.<sup>42</sup> The observation of this effect along with the kink effect in our wafer-scale GFETs indicates the high intrinsic quality of the grown graphene.

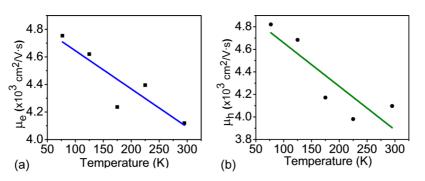

The temperature-dependent mobility of electrons and holes and the transport curves of a representative GFET ( $W = 3 \mu m$ ,  $L = 9 \mu m$ ) at 78–300 K are presented in Figure 6a and b and Figure S6. The observed mobility increases by  $\sim$ 20% when the temperature is reduced to 78 K, suggesting that electron-phonon scattering is a significant scattering mechanism. A second device with lower room-temperature mobility and higher residual carrier density showed weaker dependence ( $\sim$ 5%) on temperature for the same range (Figure S7a,b). This suppressed temperature-dependence behavior suggests that the dominant scattering mechanism is likely to be charged impurities.<sup>36,43</sup> We observed a more symmetric V-shape transport characteristic from the four-probe GFETs after high vacuum (10<sup>-6</sup> Torr) pumping for several hours (Figure S7c), resulting in the desorption of moisture and volatile adsorbates.<sup>44</sup>

Given the high average carrier mobility and demonstrated current saturation at room ambient, the

Figure 6. (a) Temperature dependence of (a) electron mobility ( $\mu_{e}$ ) and (b) hole mobility ( $\mu_{h}$ ) of a representative four-probe GFET ( $W = 3 \mu m$ ,  $L = 6 \mu m$ ) from 78 to 300 K. Transport curves of this device and a second GFET from 78 to 300 K are shown in Figures S5 and S6.

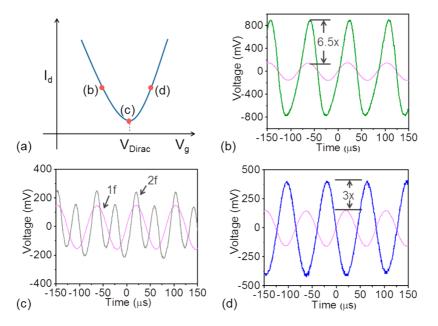

Figure 7. (a) Schematic of an  $I_d - V_q$  curve showing the corresponding applied gate bias for (b) noninverting amplification, (c) frequency doubler, and (d) inverting amplification. The pink curve represents the input signal.

wafer-scale high-performance GFETs are suitable for analog applications such as amplifiers and nonlinear high-frequency devices.<sup>45–47</sup> A triple-mode singletransistor amplifier is demonstrated based on the wafer-scale back-gated GFETs. Examples of a frequency doubler and noninverting and inverting commonsource amplifiers are presented in Figure 7b-d. A schematic of the circuit is presented in Figure S8. The supply voltage, V<sub>DD</sub>, was set to 500 mV for lowpower operation with a load impedance of 1 M $\Omega$ .  $V_{\alpha}$  is the combination of a fixed dc voltage and a small sinusoidal ac signal provided by a function generator. The input frequency, which is limited by the measurement setup, was 12 kHz. The gate bias of the GFET was adjusted to be in the hole or electron branch or ambipolar point for noninverting or inverting commonsource amplifiers or frequency amplification, respectively (Figure 7a). Here a  $6.5 \times$  voltage gain for the hole branch (Figure 7b), with the expected noninverting amplifier response, and a  $3 \times$  gain for the electron branch (Figure 7d), between the output (at the drain)

RAHIMI ET AL.

and input (at the gate), are demonstrated. The mismatch in the gain of the electron and hole branch is possibly due to the asymmetry of the transport characteristics of the device at room ambient. Once the device was biased at the minimum conduction point, the input signal sees a positive gain in its positive phase and a negative gain in its negative phase, resulting in frequency doubling. Figure 7c demonstrates the frequency doubling with an input signal of 12 kHz and output signal of 24 kHz.

## CONCLUSIONS

In summary, we have demonstrated the state-ofthe-art on scalable CVD polycrystalline graphene synthesis, device yield, and electrical statistics featuring outstanding wafer-scale devices with performance benchmarking exceeding that of previous wafer-scale polycrystalline graphene and recent reports on CVD single-crystalline graphene on hydrogen-terminated germanium substrates and epitaxially grown graphene on SiC substrates. The successful integration of CVD

VOL.8 • NO.10 • 10471-10479 • 2014

IAI

graphene on a wafer scale is achieved by not only enhancing the performance of individual graphene devices but also uniform performance across many devices. Importantly, graphene with high material guality has been scaled from 100 mm to state-of-theart 300 mm commercial Si wafers, which addresses one of the grand challenges for a future graphene-Si nanotechnology. Our CMOS-compatible device fabrication process achieved a yield of 74% with charge mobility, contact resistance, and sheet resistance superior to existing reports on the wafer-scale GFETs. The observation of a soft saturation effect and the demonstration of frequency doubler and analog amplifiers based on wafer-scale graphene make GFETs suitable for analog and high-frequency circuit applications.

### **METHODS**

Synthesis and Transfer. The graphene synthesis procedure was carried out in an AIXTRON BM300T CVD system with a cold-wall chamber and a substrate and a showerhead heater setup at 750-800 °C for 300 mm graphene synthesis. The growth substrates consist of ~500-900 nm copper film on commercially available 300 nm thermally grown SiO<sub>2</sub> on a Si wafer. The complete graphene growth processing time on 300 mm wafers is 22 min including 2 min of annealing (H $_2$  ambient, flow rate 1000 sccm, pressure 25 mbar) and 3 min of growth (CH<sub>4</sub> ambient, flow rate 10 sccm) with an automated wafer transfer in and out of the process chamber at 600 °C.

Raman spectroscopy mapping data on graphene grown on 150 mm Cu substrates are collected using a 442 nm laser (Renishaw inVia) with a focal point size of 2  $\mu m$  and on 300 mm substrates using a 457 nm laser with a focal point size of 0.9  $\mu$ m, under ambient conditions. Mapping data were analyzed using GRISP software (https://nanohub.org/tools/grisp/).4

Graphene grown on a 100 mm substrate was transferred to a 90 nm SiO<sub>2</sub> substrate by selective etching of a Cu film using an ammonium persulfate ((NH<sub>4</sub>)<sub>2</sub>S<sub>2</sub>O<sub>8</sub>) aqueous solution. A 200 nm thick PMMA film (Mw 495 000 from Sigma-Aldrich) was used as a support layer for transferring the graphene to a SiO<sub>2</sub> substrate.

Device Fabrication and Analysis. The device fabrication was performed in our 100 mm cleanroom line. The graphene is coated with a 450 nm thick positive photoresist. Microposit S1805, and patterned using the UV photolithography process followed by O<sub>2</sub> plasma etching (200 mbar, 50 W) for 50 s. The metal stack of 2 nm Ti and 48 nm Pd is deposited by lift-off with 300 nm lift-off resist (Microchem LOR 3B) and 450 nm S1805 positive resist at room temperature.

Conflict of Interest: The authors declare no competing financial interest.

Acknowledgment. This work was supported in part by the NSF CAREER award (D.A), the NSF-NASCENT Engineering Research Center (Cooperative Agreement No. EEC-1160494), and the Nanoelectronics Research Initiative (NRI) Southwest Academy of Nanoelectronics (SWAN) Center. The fabrication was conducted at the Microelectronics Research Center (MRC) at the University of Texas at Austin, which is a member of the National Nanotechnology Infrastructure Network (NNIN). The AIXTRON authors acknowledge that the work shown here has received partial funding from the European Union Seventh Framework Programme (FP7/2007-2013) under grant agreement No. FP7-285275

Supporting Information Available: Table S1. Temperature readings of sensors located at three different regions of the substrate. Figure S1. Process steps for growing graphene and their corresponding time scales. Figure S2. Images of the 100 to 300 mm substrates used for growing graphene. Figure S3. Large-area Raman mapping of graphene on 150 mm Cu substrates. Figure S4.5–95% distributions of mobility and R<sub>contact</sub> at five locations on a 100 mm wafer. Figure S5. Sheet resistance of  $\sim$ 70 GFETs measured at different back-gate voltages. Figure S6. Electrical transport curves at different temperature steps in the 78-300 K range. Figure S7. Temperature-dependence of electron mobility and hole mobility of a second four-probe GFET and electrical transport curves of the same device at different temperature steps in the 78-300 K range. Figure S8. Circuit schematic of GFET frequency doubler. This material is available free of charge via the Internet at http://pubs.acs.org.

#### **REFERENCES AND NOTES**

- 1. Schwierz, F. Graphene Transistors: Status, Prospects, and Problems. Proc. IEEE 2013, 101, 1567-1584.

- 2. Han, S. J.; Garcia, A. V.; Oida, S.; Jenkins, K. A.; Haensch, W. High-Performance Multi-Stage Graphene Radio Frequency Receiver Integrated Circuit. Nat. Commun. 2014, 5.1-6

- 3. Chen, X.; Akinwande, D.; Lee, K. J.; Close, G. F.; Yasuda, S.; Paul, B. C.; Fujita, S.; Kong, J.; Phillip, H. S. Fully Integrated Graphene and Carbon Nanotubes Interconnects for Gigahertz High-Speed CMOS Electronics. IEEE Trans. Electron Devices 2010, 57, 3137-3143.

- Lemme, M. C.; Echtermeyer, T. J.; Baus, M.; Kurz, H. A Graphene Field-Effect Device. IEEE Electron Device Lett. 2007, 28, 282-284.

- Liu, M.; Yin, X.; Ulin-Avila, E.; Geng, B.; Zentgraf, T.; Ju, L.; Wang, F.; Zhang, X. A Graphene-Based Broadband Optical Modulator. Nature 2011, 474, 64-67.

- Tao, L.; Lee, J.; Li, H.; Piner, R. D.; Ruoff, R. S.; Akinwande, D. 6. Inductively Heated Synthesized Graphene with Record Transistor Mobility on Oxidized Silicon Substrates at Room Temperature. Appl. Phys. Lett. 2013, 183115-1-4.

- 7. Bae, S.; Kim, H.; Lee, Y.; Xu, X.; Park, J. S.; Zheng, Y.; Balakrishnan, J.; Lei, T.; Kim, H. R.; Song, Y.; et al. Roll-to-Roll Production of 30-in. Graphene Films for Transparent Electrodes. Nat. Nanotechnol. 2010, 5, 574-578.

- Kim, J.; Park, H.; Hannon, J. B.; Bedell, S. W.; Fogel, K.; 8. Sadana, D. K.; Dimitrakopoulos, C. Layer-Resolved Graphene Transfer via Engineered Strain Layers. Science 2013, 342, 833-836.

- 9. Lee, Y.; Bae, S.; Jang, H.; Jang, S.; Zhu, S. E.; Sim, S. H.; Song, Y. I.; Hong, B. H.; Ahn, J. H. Wafer-Scale Synthesis and Transfer of Graphene Films. Nano Lett. 2010, 10, 490-493.

- Lee, J. H.; Lee, E. K.; Joo, W. J.; Jang, W.; Kim, B. S.; Lim, J. Y.; Choi, S. H.; Ahn, S. J.; Ahn, J. R.; Park, M. H.; et al. Wafer-Scale Growth of Single Crystal Monolayer Graphene on Reusable Hydrogen-Terminated Germanium. Science 2014, 344, 286-289

- 11. Gao, L.; Ni, G. X.; Liu, Y.; Liu, B.; Castro Neto, A. H.; Loh, K. P. Face-to-Face Transfer of Wafer-Scale Graphene Films. Nature 2014, 505, 190-194,

- 12. Tao, L.; Lee, J.; Holt, M.; Chou, H.; McDonnell, S. J.; Ferrer, D. A.; Babenco, M. G.; Wallace, R. M.; Banerjee, S. K.; Ruoff, R.S.; et al. Uniform Wafer-Scale Chemical Vapor Deposition of Graphene on Evaporated Cu (111) Film with Quality Comparable to Exfoliated Monolayer. J. Phys. Chem. C 2012, 116, 24068-24074.

- 13. Heo, J.; Chung, H. J.; Lee, S. H.; Yang, H.; Shin, J.; Chung, U. I.; Seo, S. Integration of High Quality Top-Gated Graphene Field Effect Devices on 150 mm Substrate. IEEE Device Res. Conf. 2011, 31-32.

- 14. Emtsev, K. V.; Bostwick, A.; Horn, K.; Jobst, J.; Kellogg, G. L.; Ley, L.; McChesney, J. L.; Ohta, T.; Reshanov, S. A.; Röhrl, J.; et al. Towards Wafer-Size Graphene Layers by Atmospheric Pressure Graphitization of Silicon Carbide. Nat. Mater. 2009, 8, 203-207.

VOL.8 • NO.10 • 10471-10479 • 2014

- 15. Dikin, D. A.; Stankovich, S.; Zimney, E. J.; Piner, R. D.; Dommett, G. H. B.; Evmenenko, G.; Nguyen, S. T.; Ruoff, R. S. Preparation and Characterization of Graphene Oxide Paper. Nature 2007, 448, 457-460.

- 16. Eda, G.; Fanchini, G.; Chhowalla, M. Large Area Ultrathin Films of Graphene Oxide as a Transparent and Flexible Electronic Material. Nat. Nanotechnol. 2008, 3, 270-274.

- 17. Li, X.; Cai, W.; An, J.; Kim, S.; Nah, J.; Yang, D.; Piner, R.; Velamakanni, A.; Jung, I.; Tutuc, E.; et al. Large Area Synthesis of High Quality and Uniform Graphene Films on Copper Foils. Science 2009, 324, 1312-1314.

- 18. Lee, J.; Ha, T. J.; Li, H.; Parrish, K. N.; Holt, M.; Dodabalapur, A.: Ruoff, R. S.: Akinwande, D. 25 GHz Embedded-Gate Graphene Transistors with High-K Dielectrics on Extremely Flexible Plastic Sheets. ACS Nano 2013, 7, 7744-7750.

- 19. Wang, X.; Tao, L.; Hao, Y.; Liu, Z.; Chou, H.; Kholmanov, I.; Chen, S.; Tan, C.; Jayant, N.; Yu, Q.; et al. Direct Delamination of Graphene for High-Performance Plastic Electronics. Small 2014, 10, 694-698.

- 20. Wood, J. D.; Schmucker, S. D.; Lyons, A. S.; Pop, E.; Lyding, J. W. Effects of Polycrystalline Cu Substrate on Graphene Growth by Chemical Vapor Deposition. Nano Lett. 2011, 11, 4547-4554.

- 21. Tao, L.; Lee, J.; Chou, H.; Holt, M.; Ruoff, R. S.; Akinwande, D. Synthesis of High Quality Monolayer Graphene at Reduced Temperature on Hydrogen-Enriched Evaporated Copper (111) Films. ACS Nano 2012, 6, 2319-2325.

- 22. Hao, Y.; Bharathi, M. S.; Wang, L.; Liu, Y.; Chen, H.; Nie, S.; Wang, X.; Chou, H.; Tan, C.; Fallahazad, B.; et al. The Role of Surface Oxygen in the Growth of Large Single-Crystal Graphene on Copper. Science 2013, 342, 720-723.

- 23. Tsen, A. W.; Brown, L.; Levendorf, M. P.; Ghahari, F.; Huang, P.Y.; Havener, R.W.; Ruiz-Vargas, C.S.; Muller, D.A.; Kim, P.; Park, J. Tailoring Electrical Transport Across Grain Boundaries in Polycrystalline Graphene. Science 2012, 336, 1143-1146

- 24. Huang, P. Y.; Ruiz-Vargas, C. S.; van der Zande, A. M.; Whitney, W. S.; Levendorf, M. P.; Kevek, J. W.; Garg, S.; Alden, J. S.; Hustedt, C. J.; Zhu, Y.; et al. Grain and Grain Boundaries in Single-layer Graphene Atomic Patchwork Quilt. Nature 2011, 469, 389-393.

- 25. Li, X.; Magnuson, C. W.; Venugopal, A.; An, J.; Won Suk, J.; Han, B.; Borvsiak, M.; Cai, W.; Velamakanni, A.; Zhu, Y.; et al. Graphene Films with Large Domain Size by a Two-Step Chemical Vapor Deposition Process. Nano Lett. 2010, 10, 4328-4334.

- 26. Sack, E. A.; Lyman, R. C.; Chang, G. Y. Evolution of the Concept of a Computer on a Slice. Proc. IEEE 1964, 52, 1713-1720.

- 27. Kim, S.; Nah, J.; Jo, I.; Shahrjerdi, D.; Colombo, L.; Yao, Z.; Tutuc, E.; Banerjee, S. K. Realization of a High Mobility Dual-Gated Graphene Field-Effect Transistor with Al<sub>2</sub>O<sub>3</sub> Dielectric. Appl. Phys. Lett. 2009, 94, 062107-1-3.

- 28 Chan, J.; Venugopal, A.; Pirkle, A.; McDonnell, S.; Hinojos, D.; Magnuson, C. W.; Ruoff, R. S.; Colombo, L.; Wallace, R. M.; Vogel, E. M. Redusing Extrinsic Performance-Limiting Factors in Graphene Grown by Chemical Vapor Deposition. ACS Nano 2012, 6, 3224-3229.

- 29. Hsu, A.; Wang, H.; Kim, K. K.; Kong, J.; Palacios, T. Impact of Graphene Interface Quality on Contact Resistance and RF Device Performance. IEEE Trans. Electron Devices 2011, 32, 1008-1010.

- 30. Pirkle, A.; Chan, J.; Venugopal, A.; Hinojos, D.; Magnuson, C. W.; McDonnell, S.; Colombo, L.; Vogel, E. M.; Ruoff, R. S.; Wallace, R. M. The Effect of Chemical Residues on the Physical and Electrical Properties of Chemical Vapor Deposited Graphene Transferred to SiO2. Appl. Phys. Lett. 2011, 99, 122108:1-3.

- 31. Ishigami, M.; Chen, J. H.; Cullen, W. G.; Fuhrer, M. S.; Williams, E. D. Atomic Structure of Graphene on SiO<sub>2</sub>. Nano Lett. 2007, 7, 1643–1648.

- 32. Robinson, J. A.; LaBella, M.; Zhu, M.; Hollander, M.; Kasarda, R.; Hughes, Z.; Trumbull, K.; Cavalero, R.; Snyder, D. Contacting Graphene. Appl. Phys. Lett. 2011, 98, 053103-1-3.

- 33. Shi, Y.; Dong, X.; Chen, P.; Wang, J.; Li, L. J. Effective Doping of Single-Layer Graphene from Underlying SiO<sub>2</sub> Substrates. Phys. Rev. B 2009, 79, 115402-1-4.

- 34. Franklin, A. D.; Han, S. J.; Bol, A. A.; Perebeinos, V. Double Contacts for Improved Performance of Graphene Transistors. IEEE Electron Device Lett. 2012, 33, 17-19.

- 35. Li, X.; Zhu, Y.; Cai, W.; Borysiak, M.; Han, B.; Chen, D.; Piner, R. D.; Colombo, L.; Ruoff, R. S. Transfer of Large-Area Graphene Films for High-Performance Transparent Conductive Electrodes. Nano Lett. 2009, 9, 4359-4363.

- 36. Tan, Y. W.; Zhang, Y.; Bolotin, K.; Zhao, Y.; Adam, S.; Hwang, E. H.; Das Sarma, S.; Stormer, H. L.; Kim, P. Measurement of Scattering Rate and Minimum Conductivity in Graphene. Phys. Rev. Lett. 2007, 99, 246803-1-4.

- 37. Eckmann, A.; Felten, A.; Mishchenko, A.; Britnell, L.; Krupke, R.; Novoselov, K. S.; Casiraghi, C. Probing the Nature of Defects in Graphene by Raman Spectroscopy. Nano Lett. 2012, 12, 3925-3930.

- 38. Huard, B.; Stander, N.; Sulpizio, J. A.; Goldhaber-Gordon, D. Evidence of the Role of Contacts on the Observed Electron-Hole Asymmetry in Graphene. Phys. Rev. B 2008, 78, 121402 - 1 - 4

- Bai, J.; Liao, L.; Zhou, H.; Cheng, R.; Liu, L.; Huang, Y.; Duan, X. 39. Top-Gated Chemical Vapor Deposition Grown Graphene Transistors with Current Saturation. Nano Lett. 2011, 11, 2555-2559

- Scott, B. W.; Leburton, J. High-Field Carrier Velocity and 40. Current Saturation in Graphene Field-Effect Transistors. 10th IEEE Conf. Nanotechnol. 2010, 655-658

- 41. Meric, I.; Han, M. Y.; Young, A. F.; Ozyilmaz, B.; Kim, P.; Shepard, K. L. Current Saturation in Zero-Bandgap, Top-Gated Graphene Field-Effect Transistors. Nat. Nanotechnol. 2008, 3, 654-659.

- 42. Parrish, K. N.; Akinwande, D. Impact of Contact Resistance on the Transconductance and Linearity of Graphene Transistors. Appl. Phys. Lett. 2011, 98, 183505:1-3.

- Chen, J. H.; Jang, C.; Xiao, S.; Ishigami, M.; Fuhrer, M. S. 43. Intrinsic and Extrinsic Performance Limits of Graphene Devices on SiO<sub>2</sub>. Nat. Nanotechnol. 2008, 3, 206-209.

- 44. Wang, X.; Li, X.; Zhang, L.; Yoon, Y.; Weber, P. K.; Wang, H.; Guo, J.; Dai, H. N-Doping of Graphene through Electrothermal Reactions with Ammonia. Science 2009, 324, 768-771

- 45. Wang, H.; Nezich, D.; Kong, J.; Palacios, T. Graphene Frequency Multipliers. IEEE Electron Device Lett. 2009, 30, 547-549

- 46. Lee, J.; Ha, T. J.; Parrish, K. N.; Chowdhury, Sk. F.; Tao, L.; Dodabalapur, A.; Akinwande, D. High-Performance Current Saturating Graphene Field Effect Transistors with Hexagonal Boron Nitride Dielectrics on Flexible Polymeric Substrates. IEEE Electron Device Lett. 2013, 34, 172–174.

- 47. Yang, X.; Liu, G.; Balandin, A. A.; Mohanram, K. Triple-Mode Single-Transistor Graphene Amplifier and Its Applications. ACS Nano 2010, 4, 5532-5538.

- Babenco, M. G.; Tao, L.; Akinwande, D. Graphene Raman 48. Imaging and Spectroscopy Processing: Characterization of Graphene Growth. Proc. SPIE 2012, 8466, 8466001-7.

www.acsnano.org